## IM6402/IM6403 **Universal Asynchronous Receiver Transmitter** (UART)

#### **FEATURES**

- Low Power Less Than 10mW Typ. at 2MHz

- Operation Up to 4MHz Clock (IM6402A)

- Programmable Word Length, Stop Bits and Parity

- Automatic Data Formatting and Status Generation

- Compatible with Industry Standard UART's (IM6402)

- On-Chip Oscillator with External Crystal (IM6403)

- Operating Voltage —

30

29 28

E TBR3

TBR2

25 TRO 24 TRE

23 TBRL 22 TBRE

21 T MR

IM6402-1/03-1: 5V IM6402A/03A: 4-11V IM6402/03: 5V

#### PIN CONFIGURATION (outline dwg DL, PL) DEPE 39 38 GND 38 CLS1 RADE RBR8 36 S8S TABLE 1 34 T CR PIN IM6402 IM6403 w/XTAL IM6403 w/EXT CLOCK TBR8 RBR5 N/C Divide Control Divide Control BREA! 32 h TBR7 TBR6 External Clock Input

RRC

19 Tri-State

22 Tri-State

40 TRC XTAL

Always Active

Always Active

XTAL

Always Active

Always Active

GND

#### GENERAL DESCRIPTION

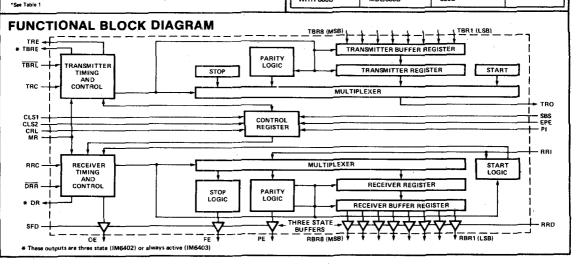

The IM6402 and IM6403 are CMOS/LSI UART's for interfacing computers or microprocessors to asynchronous serial data channels. The receiver converts serial start, data, parity and stop bits to parallel data verifying proper code transmission, parity, and stop bits. The transmitter converts parallel data into serial form and automatically adds start, parity, and stop bits.

The data word length can be 5, 6, 7 or 8 bits. Parity may be odd or even, and parity checking and generation can be inhibited. The stop bits may be one or two (or one and one-half when transmitting 5 bit code). Serial data format is shown in Figure 6.

The IM6402 and IM6403 can be used in a wide range of applications including modems, printers, peripherals and remote data acquisition systems. CMOS/LSI technology permits clock frequencies up to 4.0MHz (250K Baud), an improvement of 10 to 1 over previous PMOS UART designs. Power requirements, by comparison, are reduced from 670mW to 10mW. Status logic increases flexibility and simplifies the user interface.

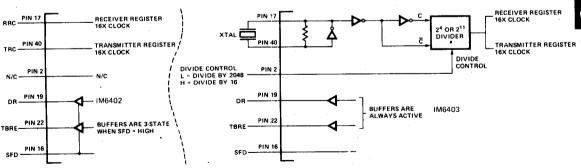

The IM6402 differs from the IM6403 in the use of five device pins as indicated in Table 1 and Figure 1.

#### ORDERING INFORMATION IM6402-1/03-1 IM6402A/03A IM6402/03 ORDER CODE IM8402/03-IPL PLASTIC PKG IM6402-1/03-1IPI IMB402/03-AIPI IM6402-1/03-11DL IM6402/03-AIDL IM6402/03IDI. CERAMIC PKG IM6402/03-AMDL MILITARY TEMP IM6402-1/03-1MDL IM6402/03-AMDL/ MILITARY TEMP. IM6402-1/03-1 883B MDL/883B WITH 883B

RBR3 [

RRR2 [

ŌΕ

SFD

DEE .

RRIC 20

## INNERSIL

### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature              |                               |

|------------------------------------|-------------------------------|

| IM6402/03                          | -40°C to +85°C                |

| Storage Temperature                | -65°C to 150°C                |

| Operating Voltage                  | 4.0V to 7.0V                  |

| Supply Voltage                     | +8.0V                         |

| Voltage On Any Input or Output Pin | 0.3V to V <sub>CC</sub> +0.3V |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

#### D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0 \pm 10\%$ ,  $T_A = -40$ °C to +85°C

|    | SYMBOL | PARAMETER                           | CONDITIONS                            | MIN                  | TYP | MAX  | UNITS |

|----|--------|-------------------------------------|---------------------------------------|----------------------|-----|------|-------|

| 1  | VIH    | Input Voltage High                  |                                       | V <sub>CC</sub> -2.0 |     |      | V     |

| 2  | VIL    | Input Voltage Low                   |                                       |                      |     | 0.8  | V     |

| 3  | IL     | input Leakage[1]                    | GND < VIN < VCC                       | -5.0                 |     | 5.0  | μА    |

| 4  | Voн    | Output Voltage High                 | I <sub>OH</sub> = -0.2mA              | 2.4                  |     |      | V     |

| 5  | VOL    | Output Voltage Low                  | I <sub>OL</sub> =1.6mA                |                      |     | 0.45 | V     |

| 6  | lork   | Output Leakage                      | GND≤V <sub>OUT</sub> ≤V <sub>CC</sub> | -5.0                 |     | 5.0  | μΑ    |

| 7  | lcc    | Power Supply Current Standby        | VIN=GND or VCC                        |                      | 1.0 | 800  | μА    |

| 8  | 'cc    | Power Supply Current IM6402 Dynamic | f <sub>C</sub> = 500 KHz              |                      |     | 1.2  | mA    |

| 9  | 'cc    | Power Supply Current IM6403 Dynamic | f <sub>crystal</sub> = 2.46MHz        |                      |     | 3.7  | mA    |

| 10 | CIN    | Input Capacitance[1]                |                                       |                      | 7.0 | 8.0  | рF    |

| 11 | co     | Output Capacitance[1]               |                                       | 1                    | 8.0 | 10.0 | pF    |

NOTE 1: Except IM6403 XTAL input pins (i.e. pins 17 and 40).

NOTE 2: V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

### A.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $C_L = 50pF$ ,  $T_A = -40$ °C to +85°C

|   | SYMBOL          | PARAMETER                   | CONDITIONS          | MIN  | TYP | MAX  | UNITS |

|---|-----------------|-----------------------------|---------------------|------|-----|------|-------|

| 1 | fc              | Clock Frequency IM6402      |                     | D,C. |     | 1.0  | MHz   |

| 2 | fcrystal        | Crystal Frequency IM6403    |                     | 1    |     | 2.46 | MHz   |

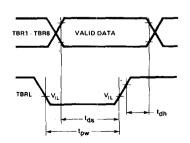

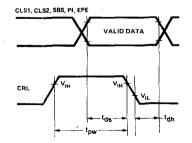

| 3 | t <sub>pw</sub> | Pulse Widths CRL, DRR, TBRL |                     | 225  | 50  |      | ns    |

| 4 | t <sub>mr</sub> | Pulse Width MR              | See Timing Diagrams | 600  | 200 |      | ns    |

| 5 | t <sub>ds</sub> | Input Data Setup Time       | (Figures 2,3,4)     | 75   | 20  |      | ns    |

| 6 | t <sub>dh</sub> | Input Data Hold Time        | <b>-</b>            | 90   | 40  |      | ns    |

| 7 | t <sub>en</sub> | Output Enable Time          |                     |      | 80  | 190  | ns    |

FIGURE 1. Functional Difference Between IM6402 and IM6403 UART (6403 has On-Chip 4/11 Stage Divider)

The IM6403 differs from the IM6402 on three Inputs (RRC, TRC, pin 2) as shown in Figure 1. Two outputs (TBRE, DR) are not three-state as on the IM6402, but are always active. The on-chip divider and oscillator allow an inexpensive crystal to be used as a timing source rather than additional circuitry such

as baud rate generators. For example, a color TV crystal at 3.579545MHz results in a baud rate of 109.2Hz for an easy teletype interface (Figure 10). A 9600 baud interface may be implemented using a 2.4576MHz crystal with the divider set to divide by 16.

### IM6402/IM6403 IM6402A/IM6403A

###

### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature               |                               |

|-------------------------------------|-------------------------------|

| Industrial IM6402AI/03AI            | -40°C to +85°C                |

| Military IM6402AM/03AM              | -55°C to +125°C               |

| Storage Temperature                 | -65°C to 150°C                |

| Operating Voltage                   | 4.0V to 11.0V                 |

| Supply Voltage                      | +12.0V                        |

| Voltage On Any Input or Output PinC | 0.3V to V <sub>CC</sub> +0.3V |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

### D.C. CHARACTERISTICS

TEST CONDITIONS: V<sub>CC</sub> = 4.0V to 11.0V, T<sub>A</sub> = Industrial or Military

|    | SYMBOL          | PARAMETER                            | CONDITIONS                                                                   | MIN                   | TYP <sup>2</sup> | MAX                 | UNITS |

|----|-----------------|--------------------------------------|------------------------------------------------------------------------------|-----------------------|------------------|---------------------|-------|

| 1  | VIH             | Input Voltage High                   |                                                                              | 70% V <sub>CC</sub>   |                  |                     | ٧     |

| 2  | VIL             | Input Voltage Low                    |                                                                              |                       |                  | 20% V <sub>CC</sub> | >     |

| 3  | IIL             | Input Leakage[1]                     | GND <vin<vcc< td=""><td>-1.0</td><td></td><td>1.0</td><td>μА</td></vin<vcc<> | -1.0                  |                  | 1.0                 | μА    |

| 4  | VOH             | Output Voltage High                  | IOH = 0mA                                                                    | V <sub>CC</sub> -0.01 | 1                |                     | ٧     |

| 5  | VOL             | Output Voltage Low                   | IOL = 0mA                                                                    |                       |                  | GND+0.01            | V     |

| 6  | OLK             | Output Leakage                       | GND < VOUT < VCC                                                             | -1.0                  |                  | 1.0                 | μА    |

| 7  | <sup>1</sup> CC | Power Supply Current Standby         | VIN=GND or VCC                                                               |                       | 5.0              | 500                 | μΑ    |

| 8  | Icc .           | Power Supply Current IM6402A Dynamic | f <sub>C</sub> = 4MHz                                                        |                       |                  | 9.0                 | mA    |

| 9  | lcc             | Power Supply Current IM6403A Dynamic | f <sub>crystal</sub> = 3.58MHz                                               |                       |                  | 13.0                | mA    |

| 10 | CIN             | Input Capacitance[1]                 |                                                                              |                       | 7.0              | 8.0                 | pF    |

| 11 | co              | Output Capacitance[1]                |                                                                              |                       | 8.0              | 10.0                | pF    |

NOTE 1: Except IM6403 XTAL input pins (i.e. pins 17 and 40).

NOTE 2: V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

### A.C. CHARACTERISTICS

**TEST CONDITIONS:**  $V_{CC} = 10.0V \pm 5\%$ ,  $C_L = 50pF$ ,  $T_A = Industrial or Military$

|   | SYMBOL          | PARAMETER                   | CONDITIONS          | MIN  | тур2 | MAX | UNITS |

|---|-----------------|-----------------------------|---------------------|------|------|-----|-------|

| 1 | fc              | Clock Frequency IM6402A     |                     | D.C. |      | 4,0 | MHz   |

| 2 | fcrystal        | Crystal Frequency IM6403A   |                     |      |      | 6.0 | MHz   |

| 3 | tpw             | Pulse Widths CRL, DRR, TBRL |                     | 100  | 40   |     | ns    |

| 4 | t <sub>mr</sub> | Pulse Width MR              | See Timing Diagrams | 400  | 200  |     | ns    |

| 5 | t <sub>ds</sub> | Input Data Setup Time       | (Figures 2,3,4)     | 40   | 0    |     | ns    |

| 6 | t <sub>dh</sub> | Input Data Hold Time        | ·                   | 30   | 30   |     | ns    |

| 7 | t <sub>en</sub> | Output Enable Time          |                     |      | 40   | 70  | ns    |

#### **TIMING DIAGRAMS**

FIGURE 2. Data Input Cycle

FIGURE 3. Control Register Load Cycle

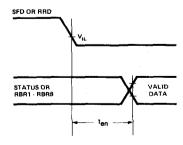

FIGURE 4. Status Flag Enable Time or Data Output Enable Time

### IM6402/IM6403

### IM6402-1/IM6403-1

## INTERSIL

### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature               |                 |

|-------------------------------------|-----------------|

| Industrial IM6402-11/03-11          | -40°C to +85°C  |

| Military IM6402-1M/03-1M            | -55°C to +125°C |

| Storage Temperature                 | -65°C to +150°C |

| Operating Voltage                   | 4.0V to 7.0V    |

| Supply Voltage                      | +8.0V           |

| Voltage On Any Input or Output Pin( |                 |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

### D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0 \pm 10\%$ ,  $T_A = Industrial or Military$

|    | SYMBOL | PARAMETER                           | CONDITIONS                                                                     | MIN                  | TYP <sup>2</sup> | MAX  | UNITS |

|----|--------|-------------------------------------|--------------------------------------------------------------------------------|----------------------|------------------|------|-------|

| 1  | VIH    | Input Voltage High                  |                                                                                | V <sub>CC</sub> -2.0 |                  |      | V     |

| 2  | VIL    | Input Voltage Low                   |                                                                                |                      |                  | 8.0  | V     |

| 3  | III.   | Input Leakage[1]                    | GND <vin<vcc< td=""><td>-1.0</td><td></td><td>1.0</td><td>μА</td></vin<vcc<>   | -1.0                 |                  | 1.0  | μА    |

| 4  | Voн    | Output Voltage High                 | I <sub>OH</sub> =-0.2mA                                                        | 2.4                  |                  |      | V     |

| 5  | VOL    | Output Voltage Low                  | I <sub>OL</sub> = 2.0mA                                                        |                      |                  | 0.45 |       |

| 6  | lolk   | Output Leakage                      | GND <vout<vcc< td=""><td>-1.0</td><td></td><td>1.0</td><td>μΑ</td></vout<vcc<> | -1.0                 |                  | 1.0  | μΑ    |

| 7  | Icc    | Power Supply Current Standby        | VIN=GND or VCC                                                                 |                      | 1.0              | 100  | μΑ    |

| 8  | Icc ·  | Power Supply Current IM6402 Dynamic | f <sub>C</sub> = 2MHz                                                          |                      |                  | 1.9  | mA    |

| 9  | licc   | Power Supply Current IM6403 Dynamic | f <sub>crystal</sub> = 3.58MHz                                                 |                      |                  | 5.5  | mA    |

| 10 | CIN    | Input Capacitance[1]                |                                                                                |                      | 7.0              | 8.0  | рF    |

| 11 | co     | Output Capacitance[1]               |                                                                                |                      | 8.0              | 10.0 | pF    |

NOTE 1: Except IM6403 XTAL input pins (i.e. pins 17 and 40).

NOTE 2:  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

### A.C. CHARACTERISTICS

**TEST CONDITIONS:**  $V_{CC} = 5.0V \pm 10\%$ ,  $C_L = 50pF$ ,  $T_A = Industrial or Military$

|   | SYMBOL          | PARAMETER                   | CONDITIONS          | MIN  | TYP2 | MAX    | UNITS |

|---|-----------------|-----------------------------|---------------------|------|------|--------|-------|

| 1 | to              | Clock Frequency IM6402      |                     | D.C. |      | 2.0    | MHz   |

| 2 | fcrystal        | Crystal Frequency IM6403    |                     |      |      | - 3.58 | MHz   |

| 3 | tow             | Pulse Widths CRL, DRR, TBRL | 1                   | 150  | 50   | ,      | กร    |

| 4 | tmr             | Pulse Width MR              | See Timing Diagrams | 400  | 200  |        | ns    |

| 5 | t <sub>ds</sub> | Input Data Setup Time       | (Figures 2,3,4)     | 50   | 20   |        | ns    |

| 6 | t <sub>dh</sub> | Input Data Hold Time        |                     | 60   | 40   |        | ns    |

| 7 | t <sub>en</sub> | Output Enable Time          |                     |      | 80   | 160    | ns    |

8

## IM6402/IM6403

| 1               |    | _  |                  |

|-----------------|----|----|------------------|

| V <sub>cc</sub> | 1  | 40 | *                |

|                 | 2  | 39 | <del>←</del> EPE |

| GND             | 3  | 38 | CLS1             |

| RRD             | 4  | 37 | GLS2             |

| RBR8            | 5  | 36 | <b>←</b> —SBS    |

| RBR7            | 6  | 35 | PI               |

| RBR6            | 7  | 34 | CRL              |

| RBR5-           | 8  | 33 | TBR8             |

| RBR4 -          | 9  | 32 | <b>←</b> —TBR7   |

| RBR3 -          | 10 | 31 | TBR6             |

| RBR2            | 11 | 30 | TBR5             |

| R8R1            | 12 | 29 | TBR4             |

| PE              | 13 | 28 | TBR3             |

| FE -            | 14 | 27 | TBR2             |

| 0E <del></del>  | 15 | 26 | TBR1             |

| SFD             | 16 | 25 | TRO              |

| *               | 17 | 24 | TRE              |

| DAR             | 18 | 23 | TORL             |

| * DR -          | 19 | 22 | TBRE *           |

| RRI             | 20 | 21 | MR               |

|                 |    |    |                  |

\*DIFFERS BETWEEN IM6402 AND IM6403.

FIGURE 5. Pin Configuration

### **IM6403 FUNCTIONAL PIN DEFINITION**

| PIN | SYMBOL.                      | DESCRIPTION                                                                                                                                                                                                                          |

|-----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | v <sub>cc</sub>              | Positive Power Supply                                                                                                                                                                                                                |

| 2   | IM6402-N/C<br>IM6403-Control | No Connection Oivide Control High: 2 <sup>4</sup> (16) Divider Low: 2 <sup>11</sup> (2048) Divider                                                                                                                                   |

| 3   | GND                          | Ground                                                                                                                                                                                                                               |

| 4   | RRD                          | A high level on RECEIVER REGISTER DISABLE forces the receiver holding register outputs RBR1-RBR8 to a high impedance state.                                                                                                          |

| 5   | RBR8                         | The contents of the RECEIVER BUFFER REGISTER appear on these three-state outputs. Word formats less than 8 characters are right justified to RBR1.                                                                                   |

| 6   | RBR7                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 7   | RBR6                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 8   | RBR5                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 9   | RBR4                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 10  | RBR3                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 11  | RBR2                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 12  | RBR1                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 13  | PE                           | A high level on PARITY ERROR indicates that the received parity does not match parity programmed by control bits. The output is active until parity matches on a succeeding character. When parity is inhibited, this output is low. |

# IM6403 FUNCTIONAL PIN DEFINITION (Continued)

|     | <del></del>                                |                                                                                                                                                                                                                                                                                                                                                             |

|-----|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | SYMBOL                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |

| 14  | FE                                         | A high level on FRAMING ERROR indicates the first stop bit was invalid. FE will stay active until the next valid character's stop bit is received.                                                                                                                                                                                                          |

| 15  | OE                                         | A high level on OVERRUN ERROR indicates the data received flag was not cleared before the last character was transferred to the receiver buffer register. The Error is reset at the next character's stop bit if DRR has been performed (i.e., DRR: active low).                                                                                            |

| 16  | SFD                                        | A high level on STATUS FLAGS DISABLE forces the outputs PE, FE, OE, DR, TBRE to a high impedance state. See Block Diagram and Figure 4.                                                                                                                                                                                                                     |

| 17  | IM6402-RRC<br>IM6403-XTAL<br>or EXT CLK IN | The RECEIVER REGISTER CLOCK is 16X the receiver data rate.                                                                                                                                                                                                                                                                                                  |

| 18  | DFIR                                       | A low level on DATA RECEIVED RESET clears the data received output (DR), to a low level.                                                                                                                                                                                                                                                                    |

| 19  | DR                                         | A high level on DATA RECEIVED indicates<br>a character has been received and trans-<br>ferred to the receiver buffer register.                                                                                                                                                                                                                              |

| 20  | RRI                                        | Serial data on RECEIVER REGISTER INPUT is clocked into the receiver register.                                                                                                                                                                                                                                                                               |

| 21  | MR                                         | A high level on MASTER RESET (MR) clears PE, FE, OE, DR, TRE and sets TBRE, TRO high. Less than 18 clocks after MR goes low, TRE returns high. MR does not clear the receiver buffer register, and is required after power-up.                                                                                                                              |

| 22  | TBRE                                       | A high level on TRANSMITTER BUFFER REGISTER EMPTY indicates the transmitter buffer register has transferred its data to the transmitter register and is ready for new data.                                                                                                                                                                                 |

| 23  | TBRL                                       | A low level on TRANSMITTER BUFFER REGISTER LOAD transfers data from inputs TBR1-TBR8 into the transmitter buffer register. A low to high transition on TBRL requests data transfer to the transmitter register. If the transmitter register is busy, transfer is automatically delayed so that the two characters are transmitted end to end. See Figure 2. |

| 24  | TRE                                        | A high level on TRANSMITTER REGISTER EMPTY indicates completed transmission of a character including stop bits.                                                                                                                                                                                                                                             |

| 25  | TRO                                        | Character data, start data and stop bits appear serially at the TRANSMITTER REGISTER OUTPUT.                                                                                                                                                                                                                                                                |

# **IM6403 FUNCTIONAL PIN DEFINITION**

(Continued).

| PIN | SYMBOL | DESCRIPTION                                                                                                                                                                                                                       |  |  |  |  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 26  | TBR1   | Character data is loaded into the TRANS-<br>MITTER BUFFER REGISTER via inputs<br>TBR1-TBR8. For character formats less<br>than 8-bits, the TBR8, 7, and 6 Inputs are<br>ignored corresponding to the program-<br>med word length. |  |  |  |  |

| 27  | TBR2   | See Pin 26 — TBR1                                                                                                                                                                                                                 |  |  |  |  |

| 28  | TBR3   | See Pin 26 — TBR1                                                                                                                                                                                                                 |  |  |  |  |

| 29  | TBR4   | See Pin 26 — TBR1                                                                                                                                                                                                                 |  |  |  |  |

| 30  | TBR5   | See Pin 26 — TBR1                                                                                                                                                                                                                 |  |  |  |  |

| 31  | TBR6   | See Pin 26 — TBR1                                                                                                                                                                                                                 |  |  |  |  |

| 32  | TBR7   | See Pin 26 — TBR1                                                                                                                                                                                                                 |  |  |  |  |

| 33  | TBR8   | See Pin 26 — TBR1                                                                                                                                                                                                                 |  |  |  |  |

| 34  | CRL    | A high level on CONTROL REGISTER LOAD loads the control register. See Figure 3.                                                                                                                                                   |  |  |  |  |

### **IM6403 FUNCTIONAL PIN DEFINITION** (Continued)

| PIN | SYMBOL                              | DESCRIPTION                                                                                                                                                         |

|-----|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35  | PI*                                 | A high level on PARITY INHIBIT inhibits parity generation, parity checking and forces PE output low.                                                                |

| 36  | SBS*                                | A high level on STOP BIT SELECT selects 1.5 stop bits for a 5 character format and 2 stop bits for other lengths.                                                   |

| 37  | CLS2*                               | These inputs program the CHARACTER LENGTH SELECTED. (CLS1 low CLS2 low 5-bits) (CLS1 high CLS2 low 6-bits) (CLS1 low CLS2 high 7-bits) (CLS1 high CLS2 high 8-bits) |

| 38  | CLS1*                               | See Pin 37 — CLS2                                                                                                                                                   |

| 39  | EPE*                                | When PI is low, a high level on EVEN PARITY ENABLE generates and checks even parity. A low level selects odd parity.                                                |

| 40  | IM6402-TRC<br>IM6403-XTAL<br>or GND | The TRANSMITTER REGISTER CLOCK is 16X the transmit data rate.                                                                                                       |

<sup>\*</sup>See Table 2 (Control Word Function)

**TABLE 2. Control Word Function**

| CONTROL WORD |      |     |     |            | DATA DITO | PARITY BIT | OTOD DIT(O) |

|--------------|------|-----|-----|------------|-----------|------------|-------------|

| CLS2         | CLS1 | Pl  | EPE | SBS        | DATA BITS | PARIIT BII | STOP BIT(S) |

| L            | Ĺ    | Γ,  | L   | L          | 5         | ODD        | . 1         |

| L            | L    | L   | L   | н          | 5         | ODD        | 1.5         |

| L            | L    | L ' | н   | Ł          | 5         | EVEN       | . 1         |

| L            | L    | L   | Н   | н          | . 5       | EVEN       | 1.5         |

| L            | L    | н   | X   | L          | 5         | DISABLED   | 1.          |

| L            | L    | Н   | ×   | н          | 5         | DISABLED   | 1.5         |

| L            | Н    | L   | L   | L          | 6         | ODD        | 1           |

| L            | . н  | L   | L   | н          | 6         | ODD        | 2           |

| L            | н    | . L | н   | L          | 6         | EVEN       | 1           |

| L.           | ļ н  | L   | Н   | Н          | 6         | EVEN       | 2           |

| L            | H,   | н   | X   | . <b>L</b> | 6         | DISABLED   | 1           |

| L            | \ н  | н   | ×   | н          | 6         | DISABLED   | 2           |

| Н            | L    | L   | L   | L          | 7         | ODD        | 1           |

| ј н          | L    | L   | L   | Н          | 7         | ODD        | 2           |

| H            | L    | L   | н   | , L        | 7         | EVEN       | 1           |

| н            | ·L   | L   | н   | н          | 7         | EVEN       | 2           |

| н -          | L    | н   | ×   | L          | 7         | DISABLED   | 1           |

| н            | L    | н   | ×   | н          | 7         | DISABLED   | 2           |

| . н          | н    | L   | L   | L          | 8         | ODD        | 1 1         |

| H            | н    | L   | L   | н          | 8         | ODD        | 2           |

| н            | н    | L   | Н   | L          | 8         | EVEN       | 1 1         |

| H            | н    | L   | н   | н          | 8         | EVEN       | 2           |

| Н            | н    | Н   | · X | L          | 8         | DISABLED   | 1 1         |

| Н            | н    | Н   | ×   | Н          | 8         | DISABLED   | 2           |

### IM6402/IM6403

### TRANSMITTER OPERATION

The transmitter section accepts parallel data, formats it and transmits it in serial form (Figure 6) on the TROutput terminal.

FIGURE 6. Serial Data Format

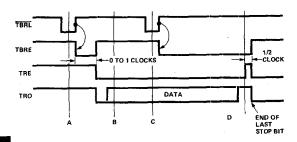

Transmitter timing is shown in Figure 7. (A) Data is loaded into the transmitter buffer register from the inputs TBR1 through TBR8 by a logic low on the TBRLoad input. Valid data must be present at least tos prior to and toh following the rising edge of TBRL. If words less than 8 bits are used, only the least significant bits are used. The character is right justified into the least significant bit, TBR1. B The rising edge of TBRL clears TBREmpty. 0 to 1 clock cycles later, data is transferred to the transmitter register, TREmpty is cleared and transmission starts. TBREmpty is reset to a logic high. Output data is clocked by TRClock, which is 16 times the data rate. CA second pulse on TBRLoad loads data into the transmitter buffer register. Data transfer to the transmitter register is delayed until transmission of the current character is complete. Data is automatically transferred to the transmitter register and transmission of that character begins.

FIGURE 7. Transmitter Timing (Not to Scale)

#### RECEIVER OPERATION

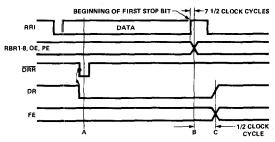

Data is received in serial form at the RI input. When no data is being received, RI input must remain high. The data is clocked by the RRClock, which is 16 times the data rate. Receiver timing is shown in Figure 8.

A low level on DRReset clears the DReady line. B During the first stop bit, data is transferred from the receiver register to the RBRegister. If the word is less than 8 bits, the unused most significant bits will be a logic low. The output character is right justified to the least significant bit RBR1. A logic high on OError indicates an overrun which occurs when DReady has not been cleared before the present character was transferred to the RBRegister. A logic high on PError indicates a parity error. 1/2 clock cycle later, DReady is set to a logic high and FError is evaluated. A logic high on FError indicates an invalid stop bit was received. The receiver will not begin searching for the next start bit until a stop bit is received.

FIGURE 8. Receiver Timing (Not to Scale)

#### START BIT DETECTION

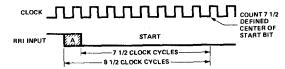

The receiver uses a 16X clock for timing (see Figure 9.) The start bit A could have occurred as much as one clock cycle before it was detected, as indicated by the shaded portion. The center of the start bit is defined as clock count  $7\frac{1}{2}$ . If the receiver clock is a symmetrical square wave, the center of the start bit will be located within  $\pm 1/2$  clock cycle,  $\pm 1/32$  bit or  $\pm 3.125\%$ . The receiver begins searching for the next start bit at the center of the first stop bit.

FIGURE 9. Start Bit Timing

#### TYPICAL APPLICATION

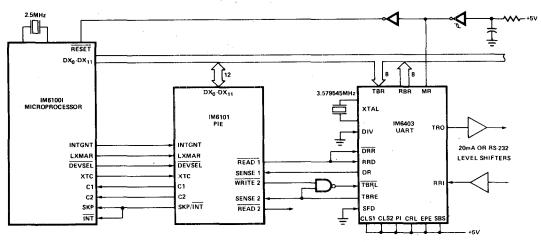

Microprocessor systems, which are inherently parallel in nature, often require an asynchronous serial interface. This function can be performed easily with the IM6402/03 UART. Figure 10 shows how the IM6403 can be interfaced to an IM6100 microcomputer system with the aid of an IM6101 Programmable Interface Element (PIE). The PIE interprets Input/Output transfer (IOT) instructions from the processor and generates read and write pulses to the UART. The SENSE lines on the PIE are also employed to allow the processor to detect UART status. In particular, the processor must know when the Receive Buffer Register has accumulated a character (DR active), and when the Transmit Buffer Register can accept another character to be transmitted.

In this example the characters to be received or transmitted will be eight bits long (CLS 1 and 2: both HIGH) and transmitted with no parity (PI:HIGH) and two stop bits (SBS:HIGH). Since these control bits will not be changed during operation, Control Register Load (CRL) can be tied high. Remember, since the IM6402/03 is a CMOS device, all unused inputs should be committed.

The baud rate at which the transmitter and receiver will operate is determined by the external crystal and DIVIDE CONTROL pin on the IM6403. The internal divider can be set to reduce the crystal frequency by either 16 (PIN 2:HIGH) or 2048 (PIN 2:LOW) times. The frequency out of the internal divider should be 16 times the desired baud rate. To generate 110 baud, this example will use a 3.579545MHz color TV crystal

INTERSIL

and DIVIDE CONTROL set low. The IM6402 may use different receive (RRC) and transmit (TRC) clock rates, but requires an external clock generator.

To ensure consistent and correct operation, the IM6402/03 must be reset after power-up. The Master Reset (MR) pin is active high, and can be driven reliably from a Schmitt trigger inverter and R-C delay. In this example, the IM6100 is reset through still another inverter. The Schmitt trigger between the processor and R-C network is needed to assure that a slow rising capacitor voltage does not re-trigger RESET. A long reset pulse after power-up (~100ms) is required by the processor to assure that the on-board crystal oscillator has sufficient time to start.

The IM6402 supports the processor's bi-directional data bus quite easily by tying the TBR and RBR buses together. A read command from the processor will enable the RECEIVER BUFFER REGISTER onto the bus by using the RECEIVER REGISTER DISABLE (RRD) pin. A write command from the processor clocks data from the bus into the TRANSMITTER BUFFER REGISTER using TBRL. Figure 10 shows a NAND gate driving TBRL from the WRITE2 pin on the PIE. This gate is used to generate a rising edge to TBRL at the point where data is

stable on the bus, and to hold TBRL high until the UART actually transfers the data to it's internal buffer. If TBRL were allowed to return low before TBRE went high, the intended output data would be overwritten, since the TBR is a transparent latch.

Although not shown in this example, the error flags (PE, FE, OE) could be read by the processor, using the other READ line from the PIE. Since an IM6403 is used, TBRE and DR are not affected by the STATUS FLAGS DISABLE pin, thus, the three error flags can be tied to the data bus and gated by connecting SFD to READ<sub>2</sub>.

If parity is not inhibited, a parity error will cause the PE pin to go high until the next valid character is received.

A framing error is generated when an expected stop bit is not received. FE will stay high after the error until the next complete character's stop bit is received.

The overrun error flag is set if a received character is transferred to the RECEIVER BUFFER REGISTER when the previous character has not been read. The OE pin will stay high until the next received stop bit after a DRR is performed.

FIGURE 10. 110 Baud Serial Interface for IM6100 System